Research Journal of Applied Sciences, Engineering and Technology 7(10): 2004-2016, 2014

DOI:10.19026/ajfst.7.492

ISSN: 2040-7459; e-ISSN: 2040-7467 © 2014 Maxwell Scientific Publication Corp.

Submitted: June 19, 2013 Accepted: July 16, 2013 Published: March 15, 2014

### **Research Article**

# Fault Analysis on VSI Fed Induction Motor Drive with Fault Tolerant Strategy

S. Nagarajan and S. Rama Reddy

Faculty of Electrical Engineering, Jerusalem College of Engineering, Anna University,

Narayanapuram Main Road, Pallikaranai, Chennai, TN 600 100, India

Abstract: The aim of this study is to design and implement a fault tolerant inverter for induction motor drive. The operations of the induction motor drives are so crucial in some applications that any fault in the drive could result in serious loss to the industry in terms of capital, process and materials not to mention the wastage due to idle labor time. Hence, it is essentials that an induction motor drive should basically be fault tolerant. This study investigates some of the possible faults in the inverter circuits by performing fault analysis on the current waveforms using harmonic spectrum. A fault tolerant system is proposed which can operate even after occurrence of the fault in runtime. A new SIMULINK model for leg swap module is proposed. The simulation studies are done using MATLAB simulation tool and the results are presented. The hardware setup is configured, tested and the experimental results are compared with the simulation results.

Keywords: Fault analysis, fault tolerant, FFT spectrum, induction motor, leg swap, open circuit, short circuit

#### INTRODUCTION

Induction Motor for many years has been regarded as workhorse in industrial applications. In the last few decades induction motor has evolved from being a constant speed motor to variable speed, variable torque machine. When the application requires large power and torque specifications, the use of induction motor essentially comes into demand. This in turn necessitates the choice and application of an efficient machine which has to meet critical requirements of stability under various fault conditions. This machine fault detection becomes an important factor that cannot be overlooked while designing the drive system.

In past decades a number of different incipient fault detection methods have been envisaged, evolved and published in papers listed here. Benbouzid (2000) presents the idea of motor current signature analysis and its application as a medium for fault detection. William and Mark (2001) explains in a concise manner the fundamental theory, main results and practical applications of motor signature analysis for the detection and the localization of abnormal electrical and mechanical conditions that indicate, or may lead to a failure of induction motors. Biswa and Das (2009) deal with harmonic analysis of motor current signatures under different fault conditions of medium and high power Variable Frequency Drive systems. Computer simulation of a VSI fed induction motor based on constant (V/f) operation is implemented using

Powersim. Bin and Andrzej (2001) proposes a simple stator fault detector for Ac motors, based on the DSP controller is presented. The detector provides compensation of the constructional and supply voltage imbalances and senses the ripple of the compensated instantaneous power. Debmalya and Ranganathan (2009) propose a CSI-fed induction motor drive scheme where GTOs are replaced by thyristors in the CSI without any external circuit to assist the turning off of the thyristors. Don et al. (2003) describes the distribution characteristics of switching the surge voltage in the stator windings of an induction motor driven by IGBT PWM inveter. Jee et al. (2006) presents an online induction motor diagnosis system using Motor Current Signature Analysis (MCSA) with advanced signal-and-data processing algorithms. MCSA is a method for motor diagnosis with statorcurrent signals. Pereira et al. (2005) presents the development and the practical implementation of a system for detection and diagnosis of intertun shotcircuits in the stator windings of induction motors. Shi et al. (1999) describes a generalized model of the threephase induction motor and its computer simulation using MATLAB. Constructional details of various submodels for the induction motor are given. Mendes et al. (2005) presents the thermal behavior of a three phase induction motor under direct torque control, when supplied by a three-phase voltage source inverter with fault tolerant capabilities. Brian et al. (2003) presents behavior of drives in fault tolerant operations and

presents different strategies for fault tolerant operations. Rodriguez *et al.* (2009) proposed a fault tolerant strategy by replacing a damaged inverter leg with an auxiliary leg. Alexander *et al.* (2010) presented a digital control architecture that demonstrates operating standby redundancy for a Voltage-Source Inverter (VSI) controller. Farzad *et al.* (2010) proposed an adaptive flux observer for concurrent estimation of rotor fluxes, unknown dc-link voltage and rotor resistance of induction motor with voltage source inverters is presented in this study. Similarly, Jorge and Antonio (2011) presented a new method for real-time diagnostics of multiple open-circuit faults in VSI feeding ac machines.

Fault Analysis of VSI fed Induction motor with leg swap module using MATLAB simulation technique has not been adopted in any of the cases of study listed in above literature. This study fills the gap by proposing a circuit model for VSI fed Induction motor drive with leg swap module, while also presenting the harmonic analysis of various fault conditions using MATLAB.

#### VSI FED INDUCTION MOTOR DRIVE

In industrial complexes, many induction motors, may often be running at no load or partial load. Hence, Proper fault analysis is needed to obtain efficient results in the fault tolerant VSI fed induction motor. This study is mainly concerned for harmonic analysis of motor current signatures for the following types of faults: open circuiting of one of the six MOSFETs gate, blowing off one MOSFET and line to ground fault at one of the motor phase terminals. Line to Line voltage can be expressed in a Fourier series recognizing that  $V_{ab}$  is shifted by  $\pi/6$  and the even harmonics are zero:

$$V_{ab} = \sum_{n=1,3,5}^{\infty} \frac{4V_s}{n\pi} \cos \frac{n\pi}{6} \sin n \left(\omega t + \frac{\pi}{6}\right)$$

(1)

$$V_{bc} = \sum_{n=1,3,5}^{\infty} \frac{4V_s}{n\pi} \cos \frac{n\pi}{6} \sin n \left( \omega t - \frac{\pi}{2} \right)$$

(2)

$$V_{ca} = \sum_{n=1}^{\infty} \frac{4V_s}{n\pi} \cos \frac{n\pi}{6} \sin n \left( \omega t - \frac{7\pi}{6} \right)$$

(3)

The line current is given by:

$$I_{a} = \sum_{n=1,3,5}^{\infty} \left[ \frac{4V_{s}}{\sqrt{3} n\pi \sqrt{R^{2} + (n\omega L)^{2}}} \cos \frac{n\pi}{6} \right] \sin (n\omega t - \theta_{n})$$

(4)

where,

$$\theta_n = \tan^{-1} \left( \frac{n \omega L}{R} \right)$$

# SIMULATION RESULTS OF HEALTHY VSI FED INDUCTION MOTOR DRIVE

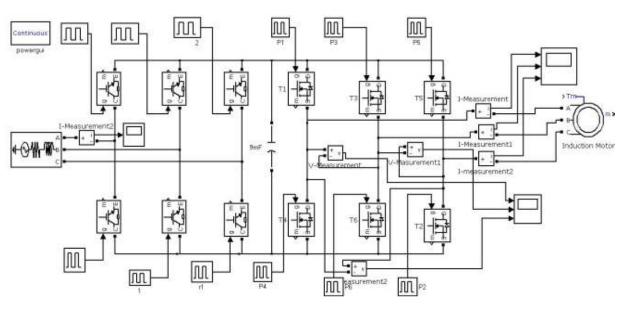

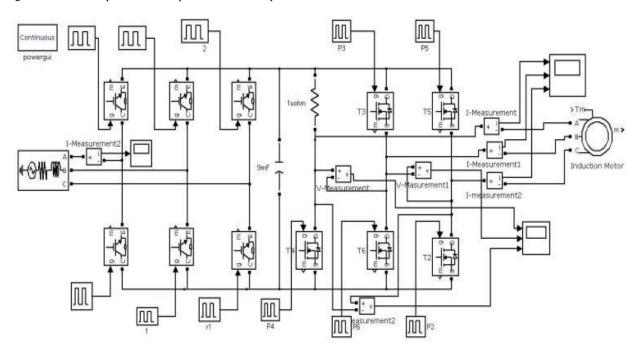

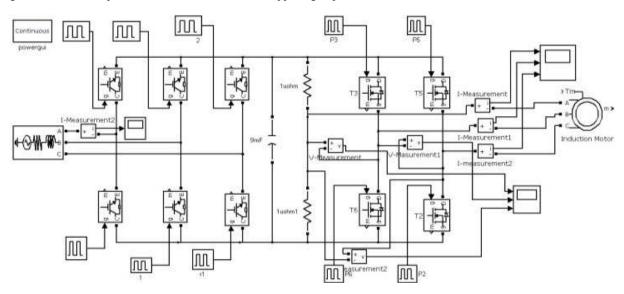

The simulation is done using the blocks of MATLAB SIMULINK and the results are presented. Circuit for the Detection of faults for three phase induction motor is simulated by using MATLAB. The SIMULINK circuit is shown in Fig. 1. The 415V AC voltage is applied to the induction motor.

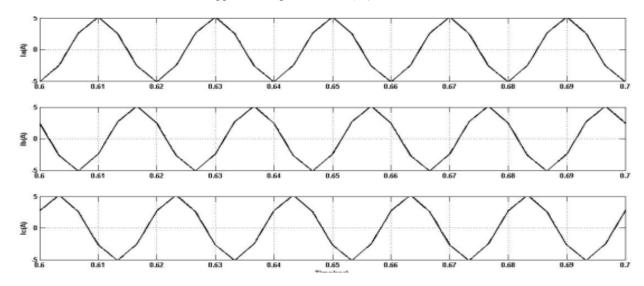

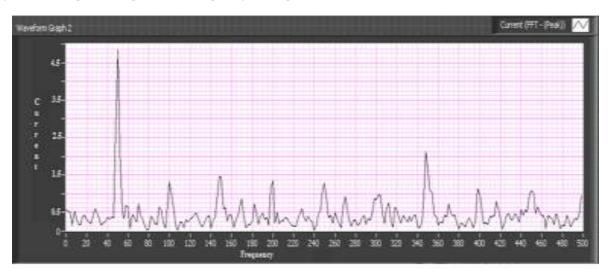

Current and voltage waveform for the three phases A, B and C at the inverter side under healthy condition are shown in Fig. 2 and 3. It is observed that under healthy condition all the line current and voltage waveforms are displaced with respect to each other.

Fig. 1: Simulation circuit for VSI-fed drive

Fig. 2: Current waveform (healthy circuit)

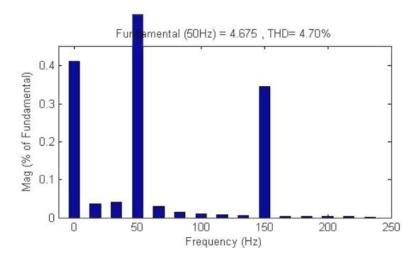

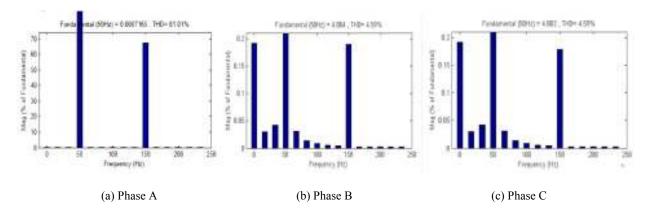

Fig. 3: Current spectrum of phase A

Fig. 4: Simulation circuit for open circuit fault in upper leg of phase A MOSFET

The Line spectrum under the healthy condition is shown in Fig. 3. Total Harmonic distortion of the phases is observed. THD value in all the Phases is 4.7%.

#### **FAULT ANALYSIS IN INVERTER**

In this section various faults are introduced in the inverter of the VSI-fed drive.

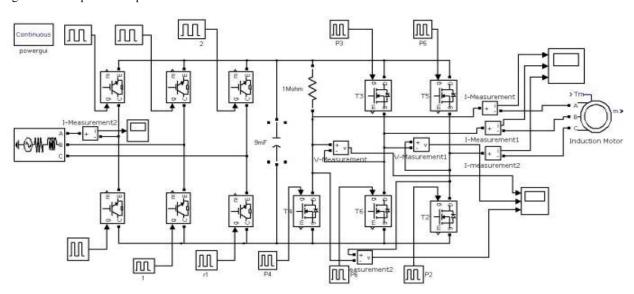

Open circuiting of upper leg of phase A MOSFET: To simulate open circuit fault, upper leg of phase A MOSFET has been replaced by a high resistance of 1 mega ohms. Introduction of the high resistance with one of the six MOSFETs is equivalent to the open circuiting of one of the six MOSFETs. The simulation circuit is shown in Fig. 4.

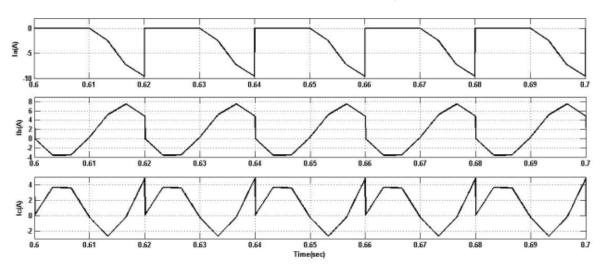

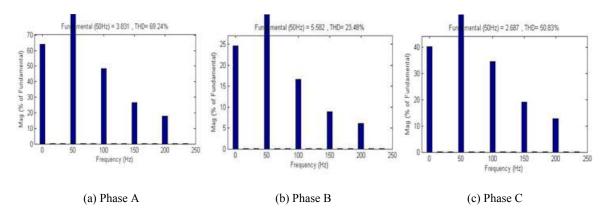

The waveforms of line Current vs. time of the three phases A, B and C under the fault conditions are shown in Fig. 5. It is observed that current direction gets reversed for Phase A. The Phase B and C waveforms are also distorted on introducing the fault. The magnitude of Current in Phase A is 3.83A, Phase B is 5.58A and Phase C is 2.68A.

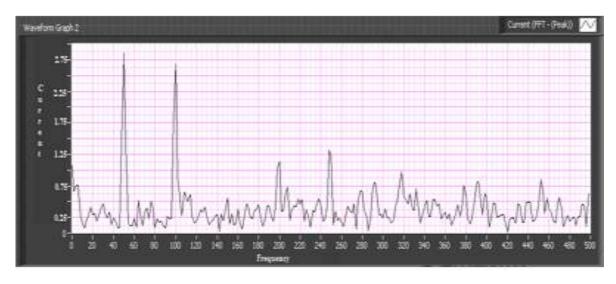

The line spectrums with phase A MOSFET open circuited in the inverter are shown in Fig. 6. The presence of DC component is significant in this fault condition. THD value in Phase A is 69%, Phase B is 23.48% and Phase C is 50.83%.

**Open circuiting of phase A:** To simulate this fault both the MOSFETs in phase A has been replaced by a high resistance of 1 Mega ohms. The simulation circuit is shown in Fig. 7.

The waveforms of line Current vs. time of the three phases A, B and C under the fault condition are shown in Fig. 8. It is observed that current in Phase A becomes zero. The Phase B and Phase C waveforms are also distorted on introducing fault. The magnitude of currents in Phase A, B and C are 0.0A, 4.08A and 4.08A, respectively.

The line spectrum for Ia, Ib and Ic with phase A MOSFET open circuited in inverter are shown in Fig. 9. Phase a current becomes zero during this fault and the symmetry of other phases is affected. THD value in Phase A is 81%, Phase B and C are 4.59%.

Fig. 5: Line current waveforms with open circuit fault in upper leg of phase A MOSFET

Fig. 6: Line current spectrum with open circuit fault in upper leg of phase A MOSFET

Fig. 7: Simulation circuit for open circuit fault in phase A

VSI Complete Open circuiting in phase A (current Waveform)

Fig. 8: Line current waveforms with open circuit fault in phase A

Short circuiting of upper leg of phase A MOSFET: To simulate short circuit fault, upper leg of phase A MOSFET has been replaced by a low resistance of 1 micro ohm. Introduction of the low resistance with one of the six MOSFETs is equivalent to the short circuiting of one of the six MOSFETs. The simulation circuit is shown in Fig. 10.

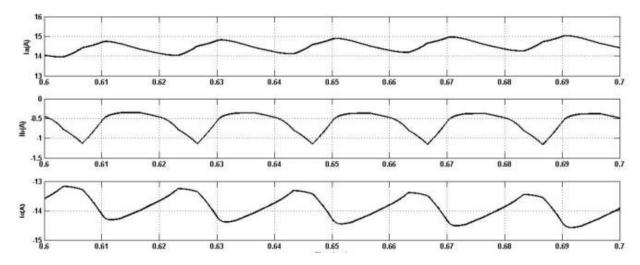

The waveforms of line Current vs. time of the three phases A, B and C under the fault conditions are shown in Fig. 11. It is observed that DC component is introduced on introducing the fault. The magnitude of fundamental Current in Phase A is 0.35A, Phase B is 0.5A and Phase C is 0.77A.

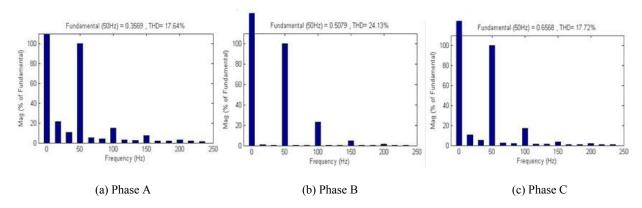

The line spectrums with phase A MOSFET short circuited in the inverter are shown in Fig. 12. The presence of DC component is significant in this fault condition. THD value in Phase A is 17%, Phase B is 24% and Phase.

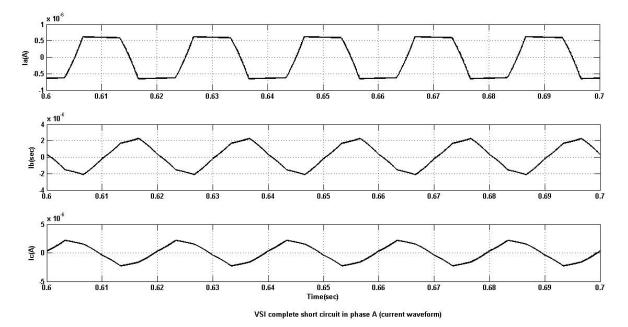

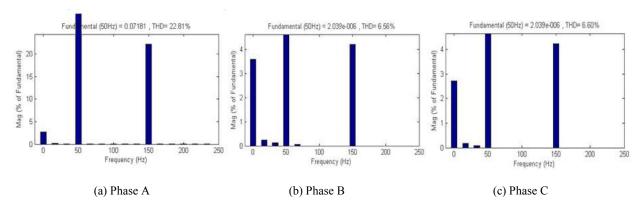

**Short circuiting of phase A:** To simulate this fault both the MOSFETs in phase A has been replaced by a low resistance of 1 micro ohm. The simulation circuit is shown in Fig. 13.

The waveforms of line Current vs. time of the three phases A, B and C under the fault condition are shown

Fig. 9: Line current spectrum with open circuit fault in phase A

Fig. 10: Simulation circuit for short circuit fault in upper leg of phase A MOSFET

Fig. 11: Line current waveforms with short circuit fault in upper leg of phase A MOSFET

Fig. 12: Line current spectrum with short circuit fault in upper leg of phase A MOSFET

Fig. 13: Simulation circuit for short circuit fault in phase A

Fig. 14: Line current waveforms with short circuit fault in phase A

Fig. 15: Line current spectrum with short circuit fault in phase A

Fig. 16: SIMULINK model for fault tolerant VSI fed induction motor drive

Table 1: Summary FFT analysis

|                                                 | Phase A     |         | Phase B     |         | Phase C     |         |

|-------------------------------------------------|-------------|---------|-------------|---------|-------------|---------|

| Condition                                       | Current (A) | THD (%) | Current (A) | THD (%) | Current (A) | THD (%) |

| Healthy                                         | 4.67        | 4.70    | 4.67        | 4.700   | 4.67        | 4.70    |

| Open circuiting of upper leg of phase A MOSFET  | 3.83        | 69.24   | 5.58        | 23.48   | 2.68        | 50.83   |

| Open circuiting of phase A                      | 0.00        | 81.01   | 4.08        | 4.59    | 4.08        | 4.59    |

| Short circuiting of upper leg of phase A MOSFET | 0.35        | 17.64   | 0.50        | 24.13   | 0.66        | 17.72   |

| Short circuiting of phase A                     | 0.07        | 22.81   | 0.00        | 6.56    | 0.00        | 6.60    |

in Fig. 14. It is observed that current in all the Phases almost zero.

The line spectrums with phase a short circuited in the inverter are shown in Fig. 15. THD value in Phase A is 22%, Phase B is 6% and Phase C is 6% (Table 1).

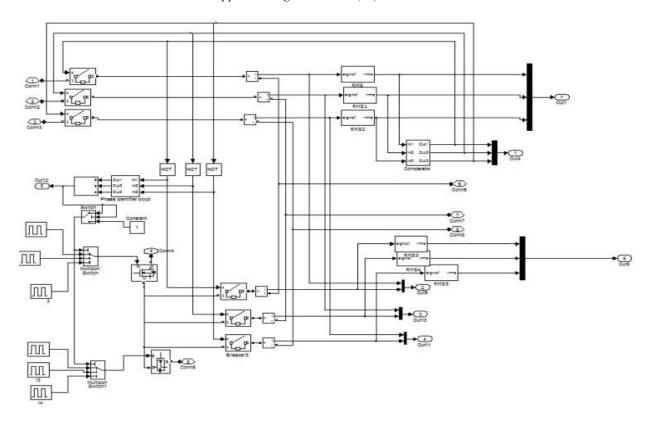

# FAULT TOLERANT VSI FED INDUCTION MOTOR DRIVE WITH LEG SWAP MODULE

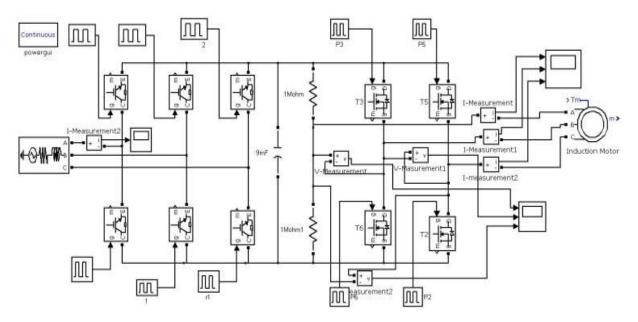

A Fault tolerant design is proposed and it is capable of operating even after the occurrence of fault. The simulation circuit is given in Fig. 16. The above

SIMULINK model includes a leg swap module which contains the auxiliary leg. The logical operator in leg swap module senses the fault current. The corresponding fault phase is identified by Phase identifier. Thus the fault Phase is isolated and replaced by auxiliary leg. The swapping is done by means of breaker. The leg swap module is presented in Fig. 17.

The proposed Leg Swap module design comprises of two important blocks:

**Logical operator:** The operation of logical operator is based on this logic (Table 2).

Fig. 17: Leg swap module used in fault tolerant inverter

Fig. 18: Logical operator

Fig. 19: Phase identifier

Table 2: Logical operator

| racio 2. Ecgioar operator |                       |

|---------------------------|-----------------------|

| Current value             | Output                |

| Ia or Ib or Ic∼0          | 0                     |

| For other values          | Output is the current |

|                           | value itself          |

Table 3: Phase identifier multiplier table

| Phase | Multiplier |

|-------|------------|

| A     | 1          |

| В     | 2          |

| C     | 3          |

| Table | <ol> <li>A com</li> </ol> | parison of | `faul | t operation | of V | SI and | fault | t tolerant \ | VSI |

|-------|---------------------------|------------|-------|-------------|------|--------|-------|--------------|-----|

|-------|---------------------------|------------|-------|-------------|------|--------|-------|--------------|-----|

|       |             |         | During fault oper | ation (fault in phase A) |                        | _                                      |  |

|-------|-------------|---------|-------------------|--------------------------|------------------------|----------------------------------------|--|

|       | Healthy VSI |         | Voltage source in | verter                   | Fault tolerant voltage | Fault tolerant voltage source inverter |  |

| Phase | Current (A) | THD (%) | Current (A)       | THD (%)                  | Current (A)            | THD (%)                                |  |

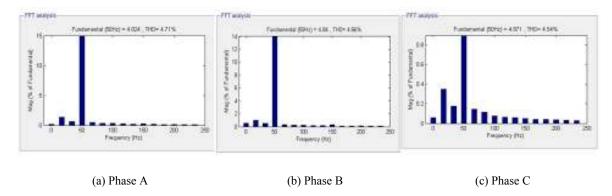

| A     | 4.67        | 4.7     | 0.038             | 81.40                    | 4.82                   | 4.71                                   |  |

| В     | 4.67        | 4.7     | 4.080             | 4.59                     | 4.84                   | 4.66                                   |  |

| C     | 4.67        | 4.7     | 4.080             | 4.59                     | 4.87                   | 4.54                                   |  |

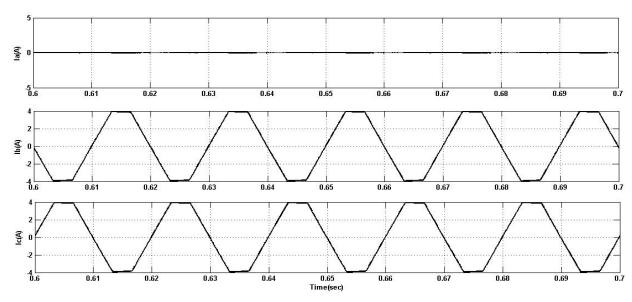

Fig. 20: Line current waveform of fault tolerant inverter during single phase open circuit fault in phase A

**Phase identifier:** Tags the signal with appropriate phase signal. (Ex: 1 for Phase A and so on.)

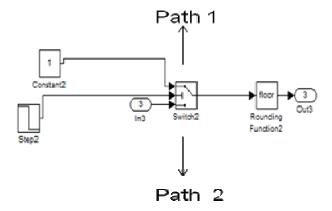

**Logical operator system:** SIMULINK model for logical operator is given in Fig. 18. In the figure, Path 1 is closed when the condition is true. Path 2 is closed when the condition is false. The condition is taken to be Control signal >= 0. A negative step signal is applied. This signal becomes negative at 0.1 sec. Hence, path 2 is closed at 0.1 sec. This time can be varied by means of step time. Till 0.1 sec, output is 1. During fault, the fault phase current is in order of mA. Hence, output is rounded to zero by means of rounding function. Output of the comparator is either 0 or 1.

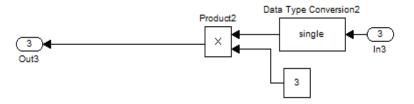

**Phase identifier:** Input signal to Phase Identifier is 1 if fault occurs in that phase. Input is converted from Boolean to single. It is multiplied based on Table 3. The output of the phase identifier is an equivalent number of fault phases such as 2 for Phase B failure.

The SIMULINK model for phase identifier is given in Fig. 19.

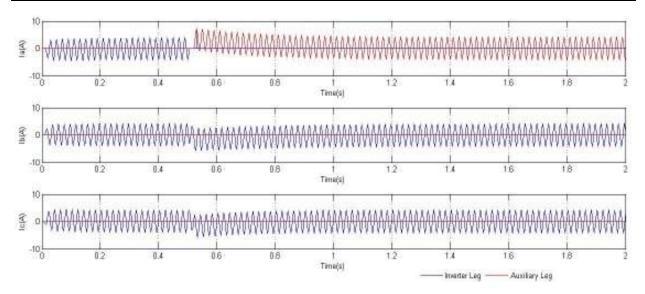

Induction motor drive structure for a reconfiguration based on auxiliary leg substitution for inverter leg fault in phase A: During single phase open circuit fault, the logical operator identifies the fault by monitoring phase current values. The breaker

of the damaged leg is open implying that the damaged leg is isolated. The auxiliary leg is then added to the inverter by means of closing its breaker. The waveforms of line current vs. time of the three phases A, B and C under Phase a open leg fault condition are shown in Fig. 20. It is observed that the line current is not zero. The line current magnitude is improved when fault tolerant inverter is introduced.

From the tabulations, it is inferred that during the single phase open circuit fault, the fault tolerant inverter was able to replicate the performance of a healthy VSI. The performance of the fault tolerant inverter was similar when the single phase open circuit fault occurs either in phase B or phase C (Table 4).

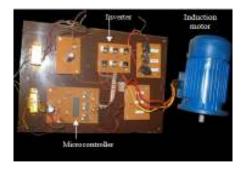

# HARDWARE RESULTS

The complete hardware set up is shown in Fig. 21. The hardware setup comprises of power circuit and a control circuit. A low cost embedded microcontroller 89C2051 is used for generating the pulses needed by the MOSFETs. MOSFET switches are used in the Power circuit of inverter. In open leg fault condition, current waveforms are distorted.

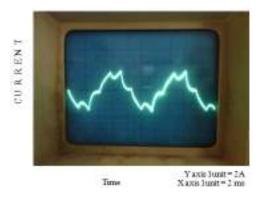

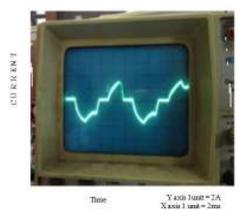

**Validation of results:** The hardware was fabricated and tested in the laboratory. The line current waveform of phase A under healthy condition is shown in Fig. 22.

Fig. 21: Line current spectrum with open circuit fault in phase A

Fig. 22: Complete hardware setup

Fig. 23: Line current of inverter with IM-load

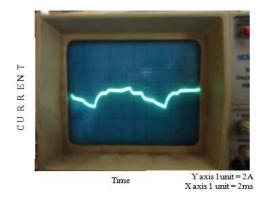

Fig. 24: Ph-A line current of inverter circuit for IM-load with open leg fault

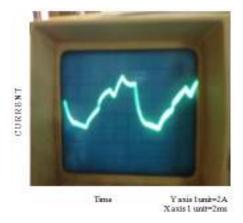

Fig. 25: Ph-B line current of inverter circuit for IM-load with open leg fault

Fig. 26: Ph-C line current of inverter circuit for IM-load with open leg fault

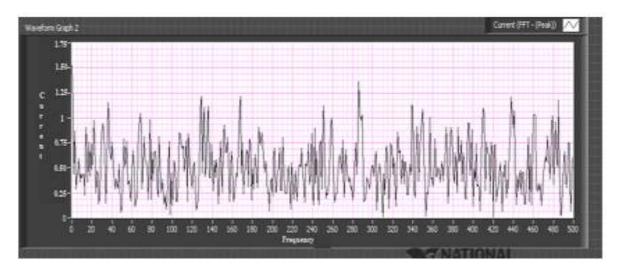

The line current wave forms of the three phases A, B and C under phase A open leg fault condition are shown in Fig. 23 to 26 respectively. The Induction motor under healthy condition runs at speed of 1420 rpm. In open leg fault condition current waveforms are observed to be distorted and the motor fails to run.

From Fig. 27 to 29, it is observed that hardware results are similar to simulation results. Summary of

Fig. 27: Current spectrum of phase-A under open leg fault in phase A

Fig. 28: Current spectrum of phase-B under open leg fault in phase A

Fig. 29: Current spectrum of phase-C under open leg fault in phase A

Table 5: Summary of hardware results

|            | Healthy    |      | Open leg fault |     |            |       |           |      |

|------------|------------|------|----------------|-----|------------|-------|-----------|------|

|            | Simulation |      | Hardware       |     | Simulation |       | Hardware  |      |

| Parameters | Amplitude  | THD  | Amplitude      | THD | Amplitude  | THD   | Amplitude | THD  |

| Ia         | 4.83A      | 4.71 | 4.81A          | 5.1 | 0.003A     | 80.40 | 0.004A    | 85.2 |

| Ia         | 4.83A      | 4.71 | 4.78A          | 5.3 | 4.23A      | 4.57  | 4.24A     | 5.1  |

| Ia         | 4.88A      | 4.52 | 4.82A          | 5.5 | 4.25A      | 4.58  | 4.51A     | 5.4  |

| Speed      | 1430       |      | 1420           |     | 0          |       | 0         |      |

hardware results is given in Table 5. From the voltage and current waveforms it is seen that the waveforms are distorted during fault condition for IM load and the IM fails to run during fault condition. From the table it is inferred that hardware results are in line with simulation results.

#### DISCUSSION AND CONCLUSION

A new SIMULINK model for inverter with leg swap module system is presented. In this study, the harmonic spectrum analysis for single phase open circuit fault of VSI fed-drive is presented. A fault tolerant design for the above mentioned fault is proposed and the results are summarized. The operation of fault tolerant system was found to be similar to the healthy operation of VSI-fed drive. The hardware is implemented using Micro controller 89 C2051, which generates the triggering pulses. The experimentally generated line voltage and current waveforms for three phase inverter with Induction motor load for healthy condition and open leg fault condition are presented. From the voltage and current waveforms it is seen that the waveforms are distorted during fault condition for IM load and the IM fails to run during fault condition. The experimental results closely agree with the simulation results. The cost is reduced since the hardware uses low cost microcontroller and leg swap module needs only two additional MOSFETs. Inverter with leg swap module is a viable alternative to the existing VSI system.

#### REFERENCES

- Alexander, L.J., O. Giovanna and T.B. Stephen, 2010. Operating standby redundant controller to improve voltage source inverter reliability. IEEE T. Ind. Appl., 46(5): 2008-2014.

- Benbouzid, M.E.H., 2000. A review of induction motors signature analysis as a medium for faults detection. IEEE T. Ind. Electron., 47(5): 984-993.

- Bin, H. and M.T. Andrzej, 2001. Simplestator fault detector for AC motors. IEEE T. Ind. Appl., 39: 192-194.

- Biswa, B. and S. Das, 2009. Current harmonics analysis of inverter-fed induction motor drive system under fault conditions. Proceeding of the International Multi Conference of Engineers and Computer.

- Brian, A.W., A.L. Thomas, M.J. Thomas and E.S. Steven, 2003. Fault tolerant three-phase AC motor drive topologies: A comparison of features, cost and limitations. Proceeding of the IEEE International Electric Machines and Drives Conference. Madison, WI, 19: 1108-1116.

- Debmalya, B. and V.T. Ranganathan, 2009. Load-commutated SCR current-source-inverter-fed induction motor drive with sinusoidal motor voltage and current. IEEE T. Power Electr., 24(4).

- Don, H.H., K.C. Lee and Y.J. Kim, 2003. Voltage stresses on stator windings of induction motors driven by IGBT PWM inverters. Proceeding of the 38th IAS Annual Conference, 1: 439-444.

- Farzad, R.S., A.N. Tooraj and J.M. Parviz, 2010. An adaptive flux observer with on-lineestimation of dclink voltage and rotor resistance for VSI-based inductionmotors. IEEET. Power Electr., 25(5): 1310-1319.

- Jee, H.J., J. Lee and B. Kwon, 2006. Online diagnosis of induction motors using MCSA. IEEE T. Ind. Electron., 53(6): 1842-1852.

- Jorge, O.E. and J.M.C. Antonio, 2011. A new approach for real time multiple open-circuit fault diagnosis. IEEE T. Ind. Appl., 47(6): 2487-2491.

- Mendes, A.M.S., X.M. López-Fernández and A.J.M. Cardoso, 2005. Thermal performance of a three-phase induction motor under fault tolerant operating strategies. Proceeding of the IEEE 36th Power Electronics Specialist Conference (PESC '05). Recife-Brazil, pp: 2886-2892.

- Pereira, L.A., G.D.Z. Silva Gaz and L.F. Pereira, 2005. Motor current signature analysis and fuzzy logic applied to the diagnosis of short-circuit faults in induction motors. Proceeding of the 32nd Annual Conference of IEEE Industrial Electronics Society (IECON 2005), pp: 6.

- Rodriguez, M.A., A. Claudio, D. Theilliol, L.G. Vela and L. Hernandez, 2009. Strategy to replace the damaged power device for fault tolerant induction motor drive. Proceeding of the International Multi Conference of Engineers and Computer.

- Shi, K.L., T.F. Chan and Y.K. Wong, 1999. Modelling and simulation of the three-phase induction motor using simulink. Int. J. Elec. Eng. Educ., 36: 163-172.

- William, T. and F. Mark, 2001. Current signature analysis to detect induction motor faults. IEEE Ind. Appl. Mag., 7(4): 26-34.