## Research Article Impact of Skin Effect, Resistive and Dielectric Losses on Current Estimation and Reliability of ULSI Interconnects

Ming Yao, Xuliang Zhang and Chaoyang Zhao Department of Electronic Engineering, University of Electronic Science and Technology of China, Chengdu, China

Abstract: In this study, a series connection system of interconnects and gates is studied. In the system, we focus on skin effect, resistive and dielectric losses in previous level interconnects and the impact of their variations on the fast current estimation and the lifetime calculation of the post level interconnects. The changes in cross-section dimensions of interconnects are used to represent their differences in resistances, dielectric losses and skin effect in actual circuits or to represent the process of Electro Migration (EM). Through the analysis of the voltage transfer function of interconnects, the different roles of skin effect, resistive and dielectric losses in signal attenuation for interconnects of various cross-sections are pointed out. The study shows that the input voltage waveforms of the post level interconnects will change if the cross-section sizes of the previous level interconnects vary. By means of showing the changing tendencies of current and lifetime estimation results affected by the cross-section dimensions of the previous interconnects, we indicate that the fast current and reliability estimation results will not be accurate enough if these effects are not included.

Keywords: Current estimation, dielectric losses, interconnect, reliability, resistive losses, skin effect

## **INTRODUCTION**

The reliability of interconnects has become one of the major concerns in nano-technology today as the scaling of chip size. The cross-section of interconnects is downsizing, while the current intensity is not decreasing proportionally, which leads to increase of the current density and interconnects are vulnerable to EM, which is the process of mass transport when metal ions and moving electrons interact with each other in high current density. It can cause voids in interconnects and make the effective cross-section area of current flow constantly shrink.

Power-ground networks have been regarded as the places where EM most likely to occur, because they are exposed to the stress of high current density in one direction. Signal wires, on the other hand, are considered to be much safer as the current in them are bidirectional. However, some recent studies showed that EM in signal wires is also serious (Nagaraj *et al.*, 1998; Blaauw *et al.*, 2003). Current parameters closely related to EM in signal lines involve the average, the root-mean-square and the peak current density  $j_{avg}$ ,  $j_{rms}$  and  $j_{peak}$ . The widely accepted Black equation relates the Median Time to Failure (MTTF) of interconnects to  $j_{avg}$  and absolute temperature T (Black, 1967). The temperature on interconnect is also influenced by Joule-Heating effect (Banerjee and Mehrotra, 2001) which is

caused by resistive power dissipation of high current density. The calculation of power dissipation in interconnects is directly relevant to  $j_{rms}$ . In addition,  $j_{peak}$  can be used to estimate short time failures caused by high current pulses.

Many manufactory processes use maximum allowed current density values as the specifications in the reliability design for signal and power networks. The corresponding current density in interconnects must be lower than these maximum allowed values to ensure that the MTTF satisfies the reliability goals (Hunter, 1997a, b). To complete the reliability design, the current values  $I_{avg}$ ,  $I_{rms}$  and  $I_{peak}$  in the networks must be calculated. Traditional time domain circuit simulators, such as SPICE, are perfect for accurate current calculations. However, the computation times of these calculators are too long for millions of current values in ULSI design. They still seem to be very time expensive even for the relatively smaller number of critical interconnect nets in reliability concern. In such circumstances, many efficient computation methods for fast estimation of current values in an interconnect tree are proposed (Blaauw et al., 2003; Shao et al., 2003a; Shao et al., 2005; Agarwal and Liu, 2007; Jain and Jain, 2011). These methods use moments to represent transfer functions of interconnect trees, signal voltages and currents (Pillage and Rohrer, 1990). Through the calculation of several lower order moments, the current

Corresponding Author: Ming Yao, Department of Electronic Engineering, University of Electronic Science and Technology of China, Chengdu, China

This work is licensed under a Creative Commons Attribution 4.0 International License (URL: http://creativecommons.org/licenses/by/4.0/).

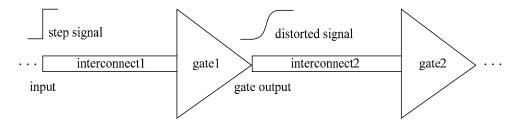

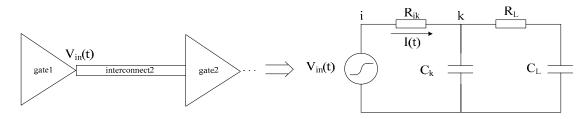

Fig. 1: The structure of a series connection of interconnects and gates

values  $I_{avg}$ ,  $I_{rms}$  and  $I_{peak}$  can be obtained, which saves a lot of computation time.

As the dimensions of interconnects decrease, their resistances keep increasing. In 32-nm process, the line resistance will be about 200 to  $800\Omega$  in upper and immediate level interconnects and in 22 nm process, the line resistance will reach as high as several kilo-ohms (ITRS, 2009). One of the consequences of the increased resistances is that high resistive losses make the propagation constant of transmitted signals become frequency dependent. At the same time, skin effect and dielectric losses lead to attenuation of the Highfrequency harmonic components (Arabi et al., 1991; Svensson and Dermer, 2001). As a result, the signals will be distorted, which is often regarded as a signal integrity problem (Zhang et al., 2009; Johnson and Graham, 2003). However, the influences of signal distortions on interconnect reliability are seldom discussed. In our study, this issue will be looked into. The structure we discuss is shown in Fig. 1. It is a series connection of interconnects and gates. The input of interconnect1 is assumed to be a step signal. After passing through interconnect1 and gate1, it becomes a distorted signal attenuated by skin effect, resistive and dielectric losses. The distorted signal is also the input of interconnect2. In actual circuits, skin effect, resistive and dielectric losses are different for different crosssection dimensions and lengths of interconnect1. At the same time, if EM occurs on interconnect1, its resistance and effective cross-section dimension will also change, which will lead to the same results. These situations of interconnect1 will cause variations in the output risetimes of gate1, thus affect the current values in interconnect2. As a result, the MTTF of interconnect 2 may not be an independent value. In addition, the previously mentioned fast current estimation methods often assume fixed or static driver output waveforms, which will result in inaccuracy in the current calculations if preceding level interconnects' impacts are not included. This study focuses on these impacts and points out that they cannot be ignored.

The transfer function of interconnects considering skin effect and dielectric losses: The transfer function of a transmission line can be denoted as (Svensson and Dermer, 2001):

$$H_0(f) = e^{-\gamma t} \tag{1}$$

$$\gamma = \sqrt{(2\pi j f L + R)(2\pi j f C)}$$

(2)

(2) includes the inductance L, the resistance R and the capacitance C of a unit length; x is the length of the line and f is the frequency. If skin effect is involved, R will become a frequency-related value as:

$$R = \frac{\rho}{A(f)} \tag{3}$$

where,

- $\rho$  = The resistivity of the metal and we take Cu as an example, so  $\rho = 1.75 \times 10^{-8} \Omega \cdot m$ .

- A(f) = The effective cross-section area of the high frequency current distribution in the interconnect and can be expressed as (Yao *et al.*, 2011):

$$A = \begin{cases} wt; \\ if \quad \delta_0^* \ge \frac{1}{2}t \\ 2\delta_0^* w; \\ if \quad \delta_0^* < \frac{1}{2}t \end{cases}$$

(4)

here,

w = The width of the interconnect

- t = The thickness of the interconnect

- $\delta_0^*$  = The effective skin depth and (Eo and William, 1993):

$$\delta_0^* = \delta \left[ 1 - \exp\left(-\frac{t}{\delta}\right) \right] \left(1 + \frac{t}{w}\right)$$

(5)

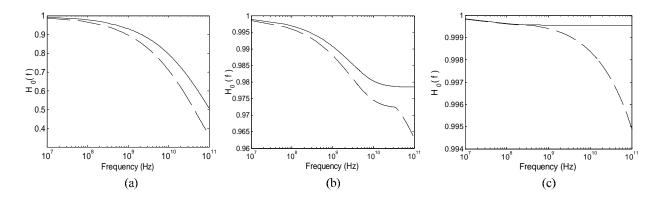

Fig. 2: The frequency domain plots of transfer functions of interconnect1. (a) (b) (c) correspond to w = 0.15, 1.5 and 15  $\mu$ m, respectively

The dashed lines: The situations in which skin effect and dielectric losses are considered; The solid lines: Do not include the two effects

$$\delta = \frac{1}{\sqrt{\pi f \mu / \rho}} \tag{6}$$

here,  $\mu$  is the permeability, which, for Cu at 20°C, is  $4\pi \times 10^{-7}$  H/m. The high frequency inductance of a unit length can be computed as (Eo and William, 1993):

$$L = \mu \frac{1}{2\pi} \ln \left[ \left( \frac{h}{0.59w} + 1.1 \right) - 0.5 + \sqrt{\left( \frac{h}{0.59w} + 1.1 \right)^2 - 1.05} \right]$$

(7)

here, h is the sum of dielectric and substrate thickness. The frequency dependent capacitance of a unit length can be denoted as (Eo and William, 1993):

$$C = C_0(f) + C_f \tag{8}$$

here,

$C_0(f) = A$  function of frequency f and it represents the high-frequency dielectric losses

$C_f$  = the fringing capacitance of rectangular interconnects

For research convenience, the ratio of w to t and the interconnect length are assumed to be fixed values, i.e., w/t = 1.5 and x = 1 mm. The line width w is changed to represent the situations of different resistances, skin effect and dielectric losses, or the occurrence of EM. In this section, we focus on the transfer function of an interconnect, for example, interconnect 1, under the variations of w. The results are shown in Fig. 2.

As can be noticed in Fig. 2, the disparities of the dashed and the solid lines indicate that the impact of

skin effect and dielectric losses on the transfer function of interconnect1 is evident. The signal attenuations of the transfer functions including skin effect and dielectric losses are larger than that of the ones calculated without the two effects and as the frequency increases the signal attenuations of the former transfer functions become stronger and stronger than that of the latter. On the other hand, at any frequency  $f_1$ , the values of  $H_0(f1)$  in (a), (b) and (c), i.e.,  $H_{0m}$  (m = a, b, c) always satisfy H<sub>0a</sub><H<sub>0b</sub><H<sub>0c</sub>. For example, when f1 = 10 GHz,  $H_0(f1)$  in (a) is 0.7, which means the attenuation of the amplitude of the signal's frequency component at this point attains 30%. In contrast,  $H_0(f1)$ in (b) and (c) are 0.973 and 0.998, respectively, which means the signal attenuations are under 5% and smaller. The major cause of the differences of the three  $H_0(f1)$ values is the dc resistances, which in (a) is as high as 1166.67 $\Omega$ , so the resistive losses in (a) are already very large without considering skin effect and dielectric losses. Even if the two effects are not included,  $H_0(fl)$ is as low as 0.77. However, the dc resistances in (b) and (c) are 11.67 and 0.12 $\Omega$ , respectively, which are much smaller, so the intrinsic resistive losses are much lower. Therefore, although the influences of skin effect and dielectric losses cannot be ignored, the transfer functions of interconnects is mainly determined by the dc resistances, i.e., the intrinsic resistive losses.

Furthermore, since the cross-section dimension of interconnect1 in (a) is too small, skin effect is still not significant even at the frequency of 100 GHz and the gap of the solid and the dashed lines is mainly resulted from the dielectric losses. In (b), the dashed curve has an apparent turn at about 30 GHz, which means skin effect becomes significant at this point and then, the curve drops much faster as a result of additional attenuations of skin effect. In (c), skin effect occurs at a

Res. J. Appl. Sci. Eng. Technol., 5(2): 619-625, 2013

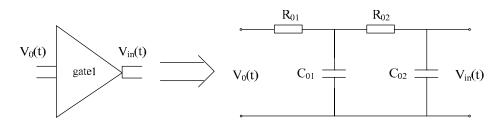

Fig. 3: The second order model of gate1

very low frequency about 400 MHz, but as the resistance of the interconnect is too small, even if the curve drops much faster after skin effect has taken place, the total signal attenuation can be ignored at 100 GHz. Therefore, the larger the cross-sections of interconnects are, the stronger the influence of skin effect is. But for future manufactory processes below several tens of nanometers, the cross-sections will be much smaller, so the attenuation of signal is mainly caused by resistive and dielectric losses and skin effect's impacts can be ignored for the frequencies bellow 100 GHz.

The gate output signal influenced by the previous level interconnect: Gate1 and interconnect1 is a series system. The gate output is the system's input response. In order to get the response, the transfer function of gate1 must also be obtained. In this study, a second order model is used to describe gate1's transfer function (Shao *et al.*, 2003b). The modal is shown in Fig. 3, where  $V_0(t)$  and  $V_{in}(t)$  are the input and the output signals of gate 1, respectively.  $R_{01}$  and  $R_{02}$  are the effective resistances of the model;  $C_{01}$  and  $C_{02}$  are the effective capacitances. Then the transfer function  $H_1(s)$  can be expressed as:

$$H_{1}(s) = \frac{\frac{1}{R_{01}R_{02}C_{01}C_{02}}}{s^{2} + \left(\frac{1}{R_{01}C_{01}} + \frac{1}{R_{02}C_{01}} + \frac{1}{R_{02}C_{02}}\right)s + \frac{1}{R_{01}R_{02}C_{01}C_{02}}}$$

(9)

Gate1 is assumed to use 0.18  $\mu$ m process. To get the unknown parameters in  $H_1(s)$ , the method of running HSPICE twice is adopted (Shao *et al.*, 2003b).

After  $H_1(s)$  has been obtained, the Fast Fourier Transform method is used to get  $V_{in}(t)$ . For research convenience, the input of interconnect1 is assumed to be a well-behaved step function defined as (Svensson and Dermer, 2001):

$$g(t) = \frac{1}{2} \left[ 1 + erf(bt) \right]$$

<sup>(10)</sup>

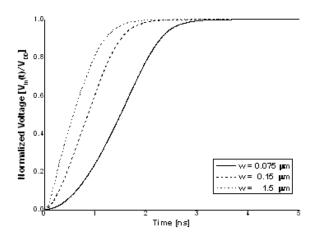

Fig. 4: Normalized  $V_{in}(t)$  for different line widths of interconnect1

Here b is a parameter giving the steepness of the step. Take G as the Fourier Transform of g(t) and combined with the transfer functions of interconnect1 and gate1, the output signal of gate1 can be obtained using the Inverse Fourier Transform:

$$V_{in}(t) = ifft \left(GH_0 H_1\right) \tag{11}$$

After some physically feasible transforms (Arabi et al., 1991; Svensson and Dermer, 2001) of the calculation in MATLAB, the waveforms of  $V_{in}(t)$  for different widths of interconnect1 are depicted in Fig. 4. The time delay of the output is ignored for it does not affect the reliability concerns of the following interconnect level. As can be seen in Fig. 4, when w = 0.075, 0.15 and 1.5  $\mu$ m, the rise time of the normalized output signal  $t_r = 1130$ , 832 and 773 ps, which means different line widths of interconnect1 will result in different waveforms of  $V_{in}(t)$ . The smaller the cross-section dimension of interconnect1 is, the longer the rise time of  $V_{in}(t)$  is. Since  $V_{in}(t)$  is the input signal of subsequent fast current estimations in interconnect 2, variations of the waveforms of  $V_{in}(t)$  will influence the calculation results.

Fig. 5: The equivalent second order circuit of interconnect2 and its load

The fast current estimation and the reliability computation results: Many waveform types are used for modeling  $V_{in}(t)$  in the fast current estimation, such as saturated ramp (Agarwal and Liu, 2007), exponential and ramp (Jain and Jain, 2011). In this study, the Weibull (Amin *et al.*, 2005) model is adopted, for its more accuracy without a significant loss in speed during timing analysis. In the frequency domain,  $V_{in}(t)$  can be denoted in the Weibull form as:

$$V_{in}(s) = W(\alpha, \beta, s) = \frac{m_0}{s} - \frac{m_1}{1!} + \frac{m_2}{2!}s - \frac{m_3}{3!}s^2 + \dots \quad (12)$$

$$m_i = \beta^i \Gamma \left( 1 + \frac{i}{\alpha} \right) \tag{13}$$

$$\Gamma(x) = \int_{0}^{\infty} y^{x^{-1}} e^{-y} dy$$

(14)

here,  $\alpha$  and  $\beta$  are the parameters that can determine the waveforms in the Weibull expression. In the fast current estimation methods, interconnect 2 and its load are equivalent to a second order circuit shown in Fig. 5.  $R_{ik}$ , which is between nodes *i* and *k*, is the resistance of interconnect 2;  $C_{k}$ , which is between node k and ground, is the capacitance of interconnect 2; I(t) is the current in interconnect 2, which is the major concern of current estimation;  $R_L$  and  $C_L$  are the resistance and capacitance of the load, respectively.

In the frequency domain, I(t) can be denoted as:

$$I(s) = \frac{V_{in}(s)}{R_{ik}} \left[ H_i(s) - H_k(s) \right]$$

(15)

Here  $H_i(s)$  and  $H_k(s)$  represent the voltage transfer functions at nodes *i* and *k* respectively and:

$$H_{i}(s) - H_{k}(s) = (m_{1}^{i} - m_{1}^{k})$$

$$s + (m_{2}^{i} - m_{2}^{k})s^{2} + (m_{3}^{i} - m_{3}^{k})s^{3} + \dots$$

(16)

here  $m_j^i$  (j = 1, 2, 3 ...) represents the *j*-th order circuit moment of node *i*. For an RC tree with no resistive path to ground, the zero order circuit moments  $m_0^i$  and  $m_0^k$ are equal to one (Jain and Jain, 2011). Let  $m_j^i - m_j^k = \Delta m_j^{ik}$  and for j = 1, 2 and 3,  $\Delta m_j^{ik}$  can be computed as (Gupta *et al.*, 1997):

$$\Delta m_1^{ik} = R_{ik} \left( C_k + C_L \right) \tag{17}$$

$$\Delta m_2^{ik} = -R_{ik}^2 (C_k + C_L)^2 - R_{ik} R_L C_L^2$$

(18)

$$\Delta m_3^{ik} = R_{ik} R_L C_L^2 \Big[ 2R_{ik} \big( C_k + C_L \big) + R_L C_L \Big]$$

(19)

Moreover, I(s) can also be expressed in the form of current moments:

$$I(s) = m_0^{ik} + m_1^{ik}s + m_2^{ik}s^2 + \dots$$

(20)

here  $m_{j}^{ik}$  (*j* = 0, 1, 2, 3 ...) is the *j*-th current moment of *I*(*s*). According to (12) to (20), the first three current moments of *I*(*s*) are:

$$m_0^{ik} = \frac{m_0 \Delta m_1^{ik}}{R_{ik}}$$

(21)

$$m_1^{ik} = \frac{m_0 \Delta m_2^{ik} - m_1 \Delta m_1^{ik}}{R_{ik}}$$

(22)

$$m_2^{ik} = \frac{m_0 \Delta m_3^{ik} - m_1 \Delta m_2^{ik} + \frac{m_2}{2} \Delta m_1^{ik}}{R_{ik}}$$

(23)

Then the current values  $I_{avg}$ ,  $I_{rms}$  and  $I_{peak}$  of interconnect2 can be obtained as (Agarwal and Liu, 2007):

$$I_{avg} = \frac{m_0^{ik}}{T_C}$$

(24)

$$I_{rms} = m_0^{ik} \sqrt{\frac{e^{-M + \frac{S^2}{4}}}{2\sqrt{\pi}ST_C}}$$

(25)

$$I_{peak} = m_0^{ik} \frac{e^{-M + \frac{S^2}{2}}}{\sqrt{2\pi}S}$$

(26)

Here

1

$$M = \ln\left[\frac{\left(m_{1}^{ik}\right)^{2}}{m_{0}^{ik}\sqrt{2m_{2}^{ik}m_{0}^{ik}}}\right]$$

$$S = \sqrt{\ln\left[\frac{2m_{2}^{ik}m_{0}^{ik}}{\left(m_{1}^{ik}\right)^{2}}\right]}$$

(27)

For illustrating purpose, let  $R_{ik} = 50\Omega$ ,  $C_{ik} = 0.5\text{pF}$ ,  $R_L = 80\Omega$ ,  $C_L = 0.3\text{pF}$  and  $T_C = 8\text{ns}$ . The duty cycle is assumed to be 0.5 and the current is assumed to return to zero after the switching event is over as nodes *i* and *k* reach their steady state values. Finally, the variations of  $I_{avg}$ ,  $I_{rms}$  and  $I_{peak}$  of interconnect2 influenced by different widths of interconnect1 can be calculated and depicted in Fig. 6.

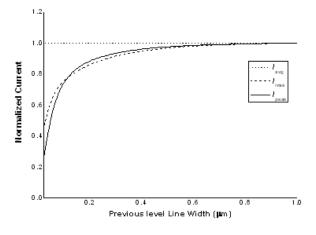

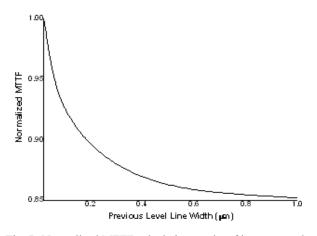

As can be seen in the picture,  $I_{avg}$  is not affected by the changes in the previous level interconnect and it is a constant. The calculated  $I_{rms}$  and  $I_{peak}$  increase with the width of interconnect1 and the curves rise very sharply in the width range of 0.02 to 0.2  $\mu$ m. When w>0.4  $\mu$ m, the upward trends of  $I_{rms}$  and  $I_{peak}$  tend to slowdown. Consequently, changes in interconnect1 due to different cross-section dimensions or EM will affect the calculation results of  $I_{rms}$  and  $I_{peak}$  in interconnect 2 and the influences will be very obvious for interconnect manufactory processes under 0.4 µm, which is the future trend. Furthermore, in Black's equation, one of the important parameters that determine the MTTF is the temperature T and it is strongly influenced by  $I_{rms}$ . In addition,  $I_{peak}$  can be used to determine the limits of the maximum current pulses interconnects can tolerate. So the variations of skin effect, resistive and dielectric losses caused by changes in previous level interconnects will influence the reliability calculation results of the current level interconnect and the impact on MTTF is depicted in Fig. 7. The normalized MTTF is computed according to the approaches of (Banerjee and Mehrotra, 2001). As is shown in the picture, the computation results of interconnect 2's MTTF have a

Fig. 6: Variations of calculated current values of interconnect2 for different line widths of interconnect1 changing from 0.02 to 1 µm

Fig. 7: Normalized MTTF calculation results of interconnect2 for different line widths of interconnect1 changing from 0.02 to 1 μm

maximum difference of about 15% as the width of interconnect1 changes from 0.02 to 1  $\mu$ m. Moreover, there is an interesting phenomenon that the smaller the cross-section size of interconnect1 is, the longer the calculated lifetime of interconnect 2 is. This phenomenon can also represent the situation of EM in interconnect 1. If the dynamic process of EM of the previous level interconnect is not considered in the fast current estimations, from the picture we can conclude that the lifetime calculation results may be pessimistic for a static input voltage waveform. Therefore, the fast current and lifetime computation methods must take these impacts into account for higher accuracy.

## CONCLUSION

In this study, the impact of skin effect, resistive and dielectric losses on the fast current estimation and the

reliability design of on-chip interconnects in a series connection system with gates has been studied. The high frequency model of the voltage transfer function of interconnects reveals that signal attenuations of interconnects are mainly determined by resistive losses and skin effect and dielectric losses will bring extra distortions to the signals. The study shows that the rise time of the input voltage waveform of the post level interconnect will increase if the cross-section size of the previous level interconnect decreases, which represents the situations of different resistances, dielectric losses and skin effect of interconnects in actual circuits or the process of EM. By showing the changing trends of the calculated current specifications  $I_{avg}$ ,  $I_{rms}$  and  $I_{peak}$  and the lifetime affected by the cross-section dimensions of the previous interconnect, we propose that the influences of skin effect, resistive and dielectric losses must be taken into consideration in the reliability models of future manufactory processes for higher accuracy.

## REFERENCES

- Agarwal, K. and F. Liu, 2007. Efficient computation of current flow in signal wires for reliability analysis. Proceeding of ICCAD, pp: 741-746.

- Amin, C.S., F. Dartu and Y.I. Ismail, 2005. Weibullbased analytical waveform model. IEEE Trans. Computer-Aided Des. of Integr. Circ. Syst., 24(8): 1156-1168.

- Arabi, T.R., A.T. Murphy, T.K. Sarkar, R.F. Harrington and A.R. Djordjevic, 1991. On the modeling of conductor and substrate losses in multiconductor, multidielectric transmission line systems. IEEE Trans. Microw. Theory Tech., 39(7): 1090-1237.

- Banerjee, K. and A. Mehrotra, 2001. Global interconnect warming. IEEE Circuits and Devices Magazine, pp: 16-32.

- Blaauw, D., O. Chanhee, V. Zolotov and A. Dasgupta, 2003. Static elec-tromigration analysis for on-ship signal interconnects. IEEE Trans. Comput-Aided Des. Integr. Circ. Syst., 22(1): 39-48.

- Black, J.R., 1967. Mass transport of aluminum by momentum exchange with conduction electrons. IEEE Intl. Reliabi. Phys. Symp., pp: 148-159.

- Eo, Y. and R.E. William, 1993. High-speed VLSI interconnect modeling based on S-Parameter measurements. IEEE Trans. Compon. Hyb. Manuf. Tech., 16(5): 555-562.

- Gupta, R., B. Tutuianu and L.T. Pileggi, 1997. The elmore delay as a bound for RC trees with generalized input signals. IEEE Trans. Comput-Aided Des., 16(1): 95-104.

- Hunter, W.R., 1997a. Self-consistent solutions for allowed interconnect current density-Part I: Implications for technology evolution. IEEE Trans. Electron Dev., 44(2): 304-309.

- Hunter, W.R., 1997b. Self-consistent solutions for allowed interconnect current density-Part II: Application to design guidelines. IEEE Trans. Elec. Dev., 44(2): 310-316.

- ITRS, 2009. Edition International Technology Roadmap for Semiconductors.

- Jain, P. and A. Jain, 2011. Accurate current estimation for interconnect reliability analysis. IEEE Trans. VLSI Syst., 99: 1-11.

- Johnson, H. and M. Graham, 2003. High-Speed Signal Propagation: A Hand-Book of Black Magic. Prentice-Hall, Englewood Cliffs, NJ.

- Nagaraj, N.S., F. Cano, H. Haznedar and D. Young, 1998. A practical approach to static signal electromigration analysis. Proceeding of 35<sup>th</sup> Design Automation Conference, pp: 572-577.

- Pillage, L.T. and R.A. Rohrer, 1990. Asymptotic waveform evaluation for timing analysis. IEEE Trans. Comput-Aided Des. Integr. Circ. Syst., 9(4): 352-366.

- Shao, M., D.F. Wong, Y. Gao, H. Cao and L.P. Yuan, 2003a. A fast and accurate method for interconnect current calculation. Proceeding of ASPDAC, pp: 37-42.

- Shao, M., M.D.F. Wong, H. Gao, Y. Gao, L.P. Yuan, L.D. Huang and S. Lee, 2003b. Explicit gate delay model for timing evaluation. Proceeding of Int. Symp. Phys. Des., pp: 32-38.

- Shao, M., Y. Gao, L.P. Yuan, H.M. Chen and M.D.F. Wong, 2005. Current calculation on VLSI signal interconnects. Proceeding of ISQED, pp: 580-585.

- Svensson, C. and G.E. Dermer, 2001. Time domain modeling of lossy interconnects. IEEE Trans. Adv. Pack., 24(2): 191-196.

- Yao, M., X. Zhang, C. Zhao and J. Ma, 2011. Selfconsistent design issues for high frequency Cu interconnect reliability incorporating skin effect. Microelec. Reliab., 55(5): 1003-1010.

- Zhang, Y., L. Zhang, A. Deutsch, G.A. Katopis, D.M. Dreps, J.F. Buckwalter, E.S. Kuh and C. Cheng, 2009. Design methodology of high performance on-chip global interconnect using terminated transmission-line. Proceeding of 10th Int. Symp. Quality Electron. Des., pp: 451-458.